# Specification

# simple pipelined bus\_\_\_\_

\_ IP-Core (VHDL)

## timing diagram

| BCLK        |                               |

|-------------|-------------------------------|

| BADDR[310]  | X Master (A) X Master (B) X X |

| BWDATA[310] | X Master (A) X Master (B) X   |

| BRDATA[310] | X Slave (A) X Slave (B) X     |

## Features

- all signals have positive logic

- similar handshaking

- easy to understand

- no overhead

- high-bandwidth

- data wide 32bit

- bidirectional /data duplex

- slave can hold bus with waitstages

- synthesizable

- byte mask for active bytes

## Applications

- system on chip

- single bus master

- data flow between moduls

#### Version: V1.0 Date: 1.10.2013

### contents

| 1 | Introduction                                                               | <b>2</b>                |

|---|----------------------------------------------------------------------------|-------------------------|

| 2 | Slave-Interface2.1Global Signals2.2Signals to Slave .2.3Signals from Slave | <b>2</b><br>2<br>2<br>2 |

| 3 | Transfer3.1typical transfer3.2Transfers with<br>waitstages                 | <b>3</b><br>3<br>3      |

| 4 | VHDL Helpers                                                               | 4                       |

| 5 | licence                                                                    | 4                       |

# 1 Introduction

This specification describes a digital bus system. It is small and very practial for use in hardware design. All signals names and valid of signals are written in this document. The bus is designed for single bus master and high-bandwidth communication with one or more slaves. The master has to decode which slave is active. All bus control signal are generated by the master.

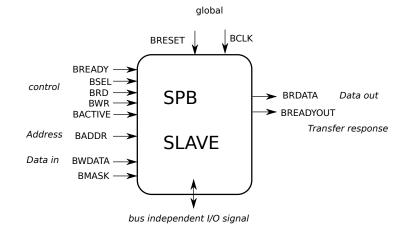

# 2 Slave-Interface

## 2.1 Global Signals

| signal | description                                                           |

|--------|-----------------------------------------------------------------------|

| BCLK   | All signals are related to rising edge of <b>BCLK</b> .               |

| BRESET | The <b>BRESET</b> is high active. Used for initial setting in slaves. |

## 2.2 Signals to Slave

| signal        | description                                                                                                                                                                                                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BADDR [31:0]  | 32-bit address                                                                                                                                                                                                                                                                                        |

| BSEL [x:0]    | The bus master decodes additional to the address a slave select signal. Each slave has an own individual bit in the array. The slave must also monitor the status of <b>HREADY</b> to ensure that the previous bus transfer has completed, If <b>HREADY</b> not high the current select is not valid. |

| BRD           | Read signal                                                                                                                                                                                                                                                                                           |

| BWR           | Write signal                                                                                                                                                                                                                                                                                          |

| BACTIVE       | new Master phase, read or write sequence                                                                                                                                                                                                                                                              |

| BMASK [3:0]   | byte mask, show transfer width and witch byte is transfered                                                                                                                                                                                                                                           |

| BWDATA [31:0] | 32bit data from master to slave                                                                                                                                                                                                                                                                       |

| BREADY        | all signals to slave are valid and the previous transfer is finished                                                                                                                                                                                                                                  |

### 2.3 Signals from Slave

| signal        | description                                                       |

|---------------|-------------------------------------------------------------------|

| BRDATA [31:0] | 32bit data from slave to master                                   |

| BREADYOUT     | Slave can indicate with zero level to get additional clock cycle. |

# 3 Transfer

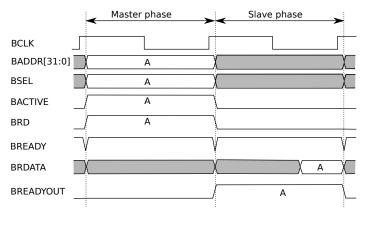

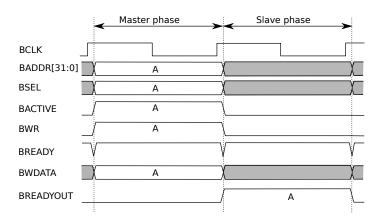

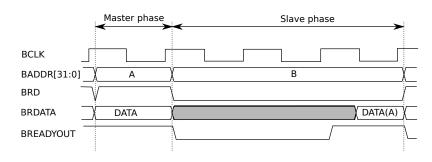

#### 3.1 typical transfer

The SPB-Bus use two phases. A master and a slave phase. The transfer is started with a master phase and this phase will change to slave phase if **BREADY** is 1. When the slave phase is on the Bus the data from slave is transferred to master. The bus is duplex. Then a slave phase is on the bus also the next master phase can be also on the bus. This technique is call pipeline. It is an optimised data troughput.

In the master phase all signals are broadcasted to slave. The resonse from slave is in the slave phase. The slave generates an acknowledge with **BREADYOUT**.

Figure 1: read transfer

Figure 2: write transfer

Each transfer has valid address and also valid control signals. Burst writes and reads are possible but each transfer is a single transfer.

### 3.2 Transfers with waitstages

Some slaves can not receive too much datas or response in the next BCLK cycle like in section typical transfer. A slave indicates with **BREADYOUT**=0 the slave phase is not finsh. The master holds on bus the next master phase valid until **BREADYOUT**=1. Wait stages are allowed in read and write transfers. But they blocking the bus and can also blocking the master. This technic should not used for a handshake. This additional clock cycles are for garante the data valid or prevent overflows in data stream.

Figure 3: read transfer with waitstages

# 4 VHDL Helpers

```

type SPB_in is

record

BADDR

: std_logic_vector (31 downto 0);

BSEL

: std_logic_vector (sel_size-1 downto 0);

BRD

: std_logic;

--READ

--WRITE

BWR

: std_logic;

BACTIVE

: std_logic;

: std_logic_vector (3 downto 0);

BMASK

BWDATA

: std_logic_vector (31 downto 0);

BREADY

: std_logic;

end record;

type SPB_out is

record

: std_logic_vector (31 downto 0);

BRDATA

BREADYOUT : std_logic;

end record;

```

# 5 licence

This document can be copied free without changing. The specification is a royalty free part but your work must attribute simple pipelined bus in use a specification by Dossmatik. Other things distributed by Dossmatik GmbH are not part of this licence.